TriCore 内核学习笔记

前段时间在 TriCore 上肝了一个月的 rt-thread 系统移植,终于初步移植成功.所以做下知识整理,本文更多关注的是如何给 TriCore 移植操作系统,整理如下:

简介

TriCore 是英飞凌半导体公司专为嵌入式实时系统设计的 32 位精简指令(RISC)的芯片架构。汽车电子上用的比较多。低中断延迟;硬件自动上下文切换 都是它的特点。

TriCore 寄存器概览

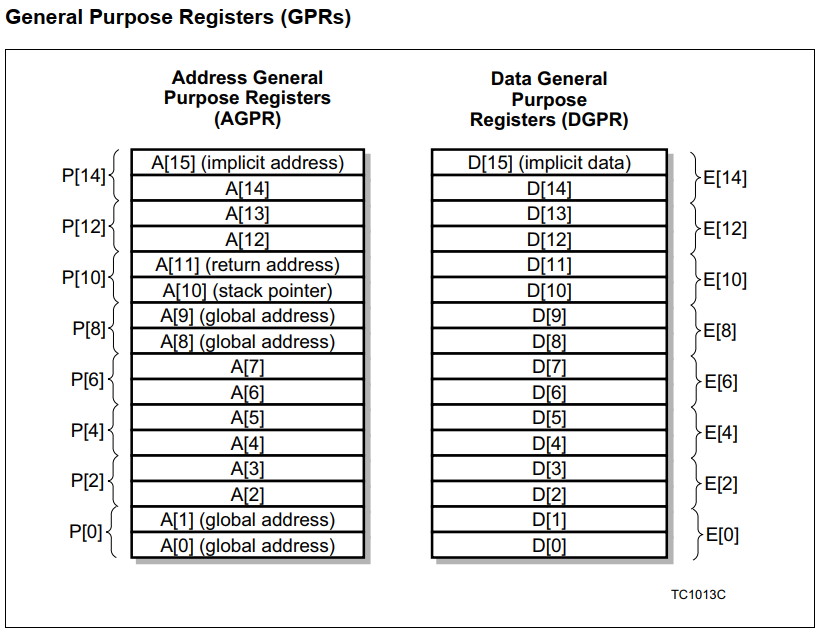

32 个通用目的寄存器

这 32 个通用目的寄存器又分为 16 个通用地址寄存器;16 个通用数据寄存器;

通用地址寄存器(A[0]-A[15])

A[0], A[1], A[8], A[9] 这四个寄存器被定义为系统全局寄存器,它们的内容不会在 调用;陷阱;中断 发生时被保存或恢复。

A[10] : 被用作栈指针寄存器(SP)。

A[11] : 被用作存储调用和链接跳转的返回地址(RA),或者用作存储中断和陷阱的返回程序计数器(PC)的值。

A[15] : 隐式地址寄存器,被很多 16 位的指令隐式的使用。有助于简化指令编码。

通用数据寄存器(D[0]-D[15])

D[15] : 隐式数据寄存器,被很多 16 位的指令隐式的使用。有助于简化指令编码。

TriCore 没有特别区分浮点通用数据寄存器,通用数据寄存器也被用于浮点操作。

系统寄存器

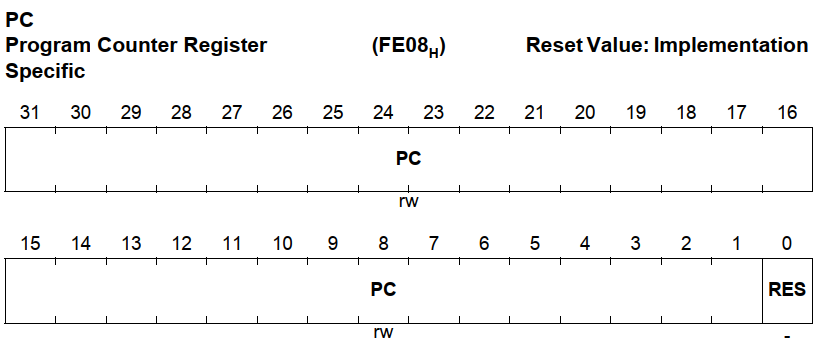

PC : 程序计数器寄存器

程序计数器 (PC) 保存着当前正在运行的指令的地址。程序计数器是任务状态信息的一部分。只有当核心停止时,PC 才会被写入。如果内核没有停止,写入将是无效的。

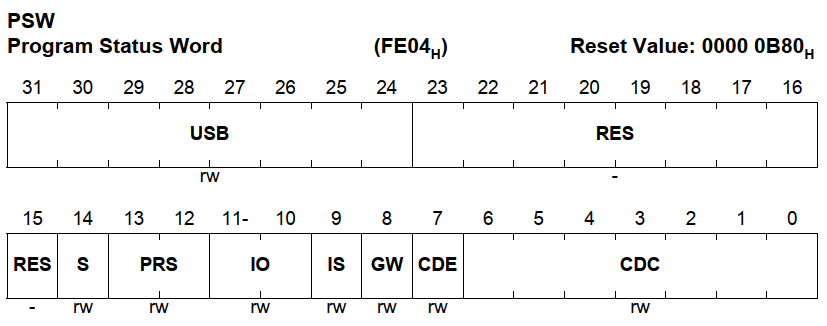

PSW : 程序状态字寄存器

- 上半部分用于保存芯片状态: 比如执行 add 指令后,溢出这些标记。

- 下半部分用于保存系统控制值:访问权限等级;函数调用深度计数;是否是中断环境下的栈指针;全局通用地址寄存器的写允许使能位。

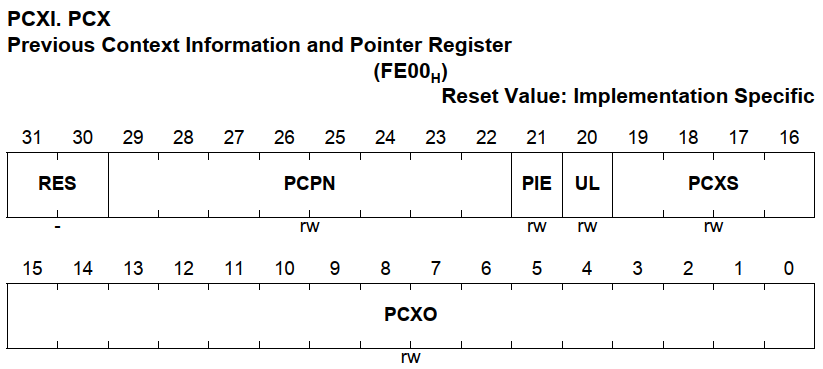

PCXI : 前一个上下文信息寄存器

这个寄存器保存了前一个上下文的信息。比如前一个线程的: CPU 优先级号;中断使能位;上下文的保存地址。保存的上下文类型。

中断系统

TriCore 有两种中断管理方式:

- 硬件管理方式

- 软件管理方式

由头文件 ifx_Cfg.h 中的 #define IFX_USE_SW_MANAGED_INT 控制中断管理方式。

中断请求的服务提供者既可以是 CPU,也可以是 DMA。

中断控制单元(ICU)的中断控制寄存器(ICR)持有当前CPU优先级号(CCPN),全局中断启用/禁用位(IE)和暂挂中断优先级号(PIPN),以及特定于实现的位来控制中断仲裁周期。

进入中断的流程

- 保存当前任务的上层 CSA,并且将当前的 PC 值赋值给 A[11] (return address)。

- 如果处理器之前没有使用中断堆栈(PSW.IS = 0),那么 A[10] (stack pointer)被赋值为 中断堆栈指针 (ISP),然后 PSW.IS = 1;

- CPU 模式设置为 Supervisor 模式,即最高权限模式。(PSW.IO = 12b)

- 设置 PSW.PRS = 00,即:中断内存保护映射???(存疑)

- 清除调用深度寄存器 CDC 的值。

- 使能调用深度计数。即 PSW.CDE = 1。

- 设置 PSW.GW = 0 。即:A[0], A[1], A[8], A[9] 全局寄存器不再被允许写入。

- 设置 ICR.IE = 0 。即:关闭全局中断。

- 访问中断向量表以获取 ISR 的第一条指令。有效地址是BIV寄存器的内容。

退出中断的流程

当ISR带着RFE (Return From Exception)指令退出时,硬件自动恢复上层上下文。上面的上下文包括保存 之前的CPU优先级号

(PCPN)和 之前的全局中断使能位(PIE)。这些位的值的用法如下:

- PCXI.PCPN写入ICR。CCPN将CPU优先级设置为中断前的数值。

- PCXI.PIE写入ICR。IE来恢复这个位的状态。

然后被中断的程序继续执行。

陷阱(trap)系统

trap 是由不可屏蔽中断(NMI)、指令异常、内存管理异常或非法访问等事件引起的。陷阱总是被激活的,不能被软件操作屏蔽。

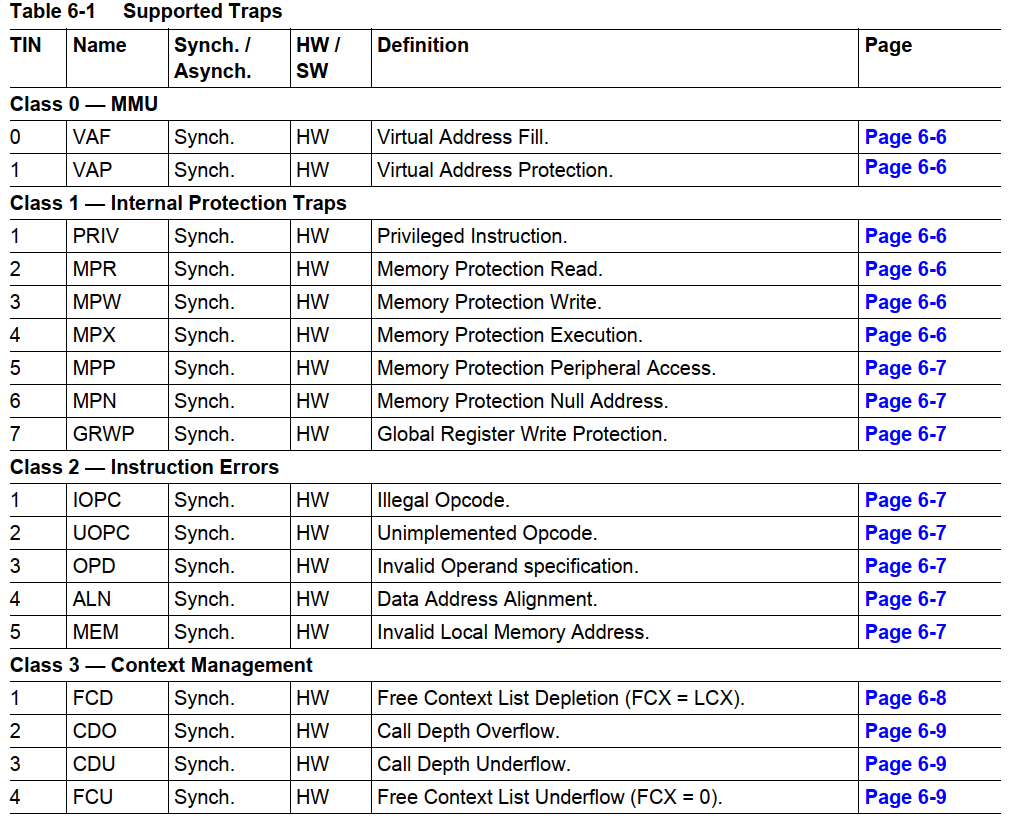

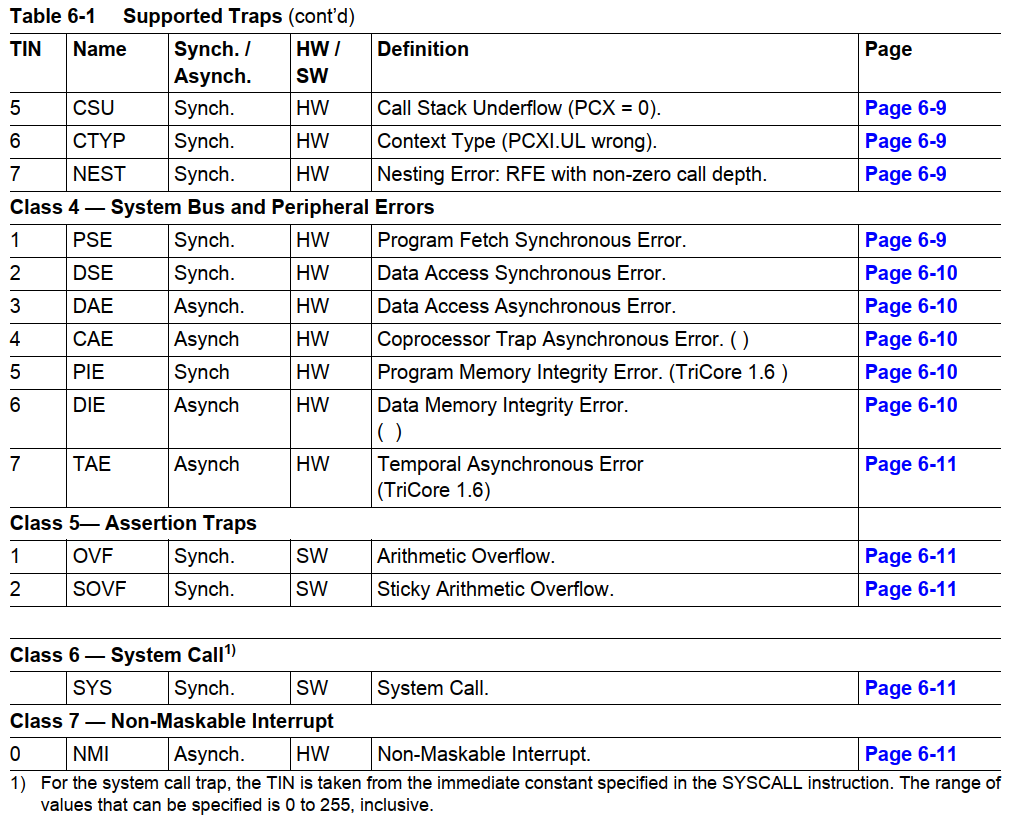

TriCore 定义了 8 种 trap 类型。每个类型的 trap 用 TIN 来区分,并且在进入 陷阱(trap)服务程序之前, TIN 的值会被赋值到 D[15] 寄存器中。

陷阱可以进一步分类为同步或异步,以及硬件或软件生成。

以下是陷阱的类型:

发生陷阱(trap)时的初始化流程

- 保存上层上下文。

- 将返回地址保存到 A[11] 寄存器中。

- 将 trap 类型(TIN)保存到 D[15] 寄存器中。

- 当 PSW.IS = 0 时,将中断栈指针赋值给 A[10] 寄存器中,然后将 PSW.IS = 1.

- CPU 模式设置为 Supervisor 模式,即最高权限模式。(PSW.IO = 12b)

- 设置 PSW.PRS = 00,即:中断内存保护映射???(存疑)

- 清除调用深度寄存器 CDC 的值。

- 使能调用深度计数。即 PSW.CDE = 1。

- 设置 PSW.GW = 0 。即:A[0], A[1], A[8], A[9] 全局寄存器不再被允许写入。

- 设置 ICR.IE = 0 。即:关闭全局中断。

- 访问 trap 向量表以获取 trap 服务例程的第一条指令。有效地址是 BTV 寄存器的内容。

TriCore 任务的概念

任务分为两种:

- SMT (Software Managed Tasks):由实时操作系统创建,调度程序管理。

- ISR (Interrupt Service Routines):处理器在收到硬件中断后直接调用的服务程序。

每一个任务都有自己的模式,一共有三种模式:

- User-0 Mode:用于不需要访问外围设备的任务。该模式不能启用或禁用中断。

- User-1 Mode:用于访问普通、不受保护的外围设备的任务。通常这将是对串行端口的读或写访问,对计时器的读访问,和大多数I/O

状态寄存器。该模式下的任务可能会在短时间内关闭中断 - Supervisor Mode::允许对系统寄存器和所有外围设备进行读/写访问。该模式下的任务可以关闭中断。

未完待续

TriCore 有自己的一套硬件上下文切换机制,这套机制虽然让线程切换的开销变小,但是让移植 rt-thread 变得稍许困难。后续我会再写篇文章讲讲 TriCore 的上下文切换机制,以及如何将 rt-thread 系统移植到 TriCore 内核的芯片上。